# LXD970A Demo Board for 10/100 and 100BASE-FX Applications

**Development Kit Manual**

January 2001

Order Number: 249103-001

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The LXD970A may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

${}^{\star}\textsc{Third-party}$  brands and names are the property of their respective owners.

| 1.0           | Gen                             | eral Description                                                                                                                                                                                                  | 5                    |

|---------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|               | 1.1                             | Features                                                                                                                                                                                                          | 5                    |

| 2.0           | Equ                             | ipment and Setup                                                                                                                                                                                                  | 7                    |

|               | 2.1<br>2.2<br>2.3               | Test Setup  Loading Test File  Power Supply Option  2.3.1 External +5V Supply for Analog Circuitry (VCCA, VCCT and                                                                                                | 8<br>d VCCR)9        |

|               | 2.4                             | Test Points                                                                                                                                                                                                       |                      |

| 3.0           | Jum                             | npers                                                                                                                                                                                                             | 10                   |

| 4.0           | Hard                            | dware Control Interface                                                                                                                                                                                           | 11                   |

| _             | 4.1                             | Multi-Function Pins                                                                                                                                                                                               |                      |

|               |                                 | 4.1.1 Function/Address Settings                                                                                                                                                                                   | 11                   |

|               | 4.2                             | LED Indicators                                                                                                                                                                                                    | 13                   |

| Figures       | 1<br>2<br>3<br>4<br>5           | LXD970A Demo BoardBasic Test SetupOptional Test SetupHardware Control Interface Jumper PlacementLXD970A Schematic                                                                                                 | 8<br>11              |

| <b>Tables</b> |                                 |                                                                                                                                                                                                                   |                      |

|               | 1<br>2<br>3<br>4<br>5<br>6<br>7 | Test Point Descriptions  Jumper Descriptions  MF Pins Input Voltage Levels  Hardware Control Interface (JP1) Functions  Operating Speed Advertisement Settings  Additional JP1 Jumper Functions  LED Descriptions | 10<br>11<br>12<br>12 |

# 1.0 General Description

The LXD970A Demo Board is a versatile 10/100Mbps Ethernet media access unit (MAU) that demonstrates all of the integral features of the LXT970A Fast Ethernet Transceiver.

The LXD970A provides a working platform for evaluation of the LXT970A Fast Ethernet Transceiver in 10BASE-T and/or 100BASE-TX/FX applications.

The LXD970A Demo Board is configured with a single chip 10/100Mbps, IEEE 802.3u compliant, Fast Ethernet Transceiver unit (LXD970A). The demo board is designed to plug into a transceiver test box via a standard 40-pin MII connector. This allows system designers to test 10Mbps and 100Mbps link performance, auto-negotiation and register functionality prior to board prototyping.

The LXT970A also provides an ECL-type interface for 100BASE-FX link testing.

This document describes typical Demo Board setup procedures for a 100BASE-TX environment.

Before using the Demo Board, review the LXT970A Fast Ethernet Transceiver data sheet for device functionality and specifications.

#### 1.1 Features

- IEEE 802.3-compliant 10BASE-T and 100BASE-TX using a single RJ45 connection.

- Quick setup, ease of use, and clear visibility of application settings for:

- Complete system demonstration

- Individual circuit isolation

- LED indicators for major functions.

- IEEE 802.3u MII interface with extended register capability.

- Configured for single 5V supply operation.

- Standard half duplex or full duplex operation at 10 or 100 Mbps.

- 100BASE-FX fiber optic capability (unstuffed optional circuitry).

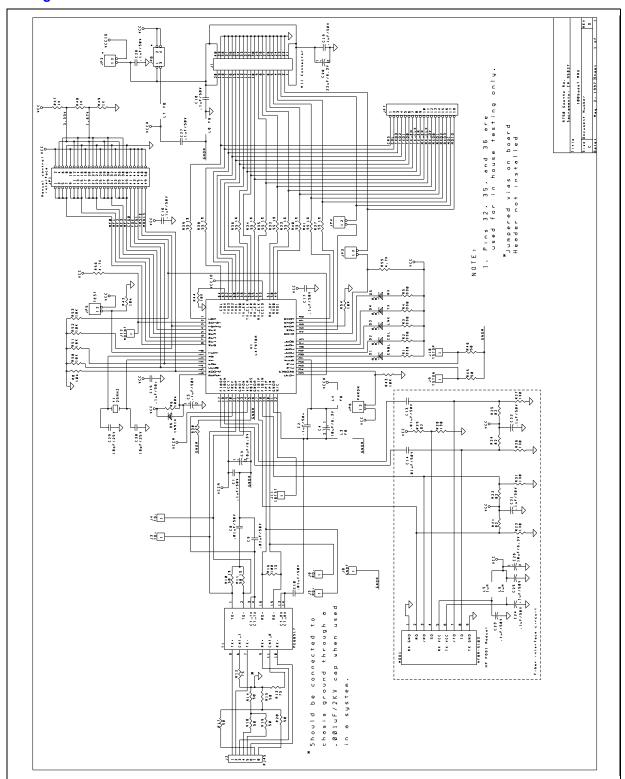

Figure 1. LXD970A Demo Board

# 2.0 Equipment and Setup

The LXD970A Demo Board includes all the components needed for a successful evaluation. However, the following additional equipment is recommended:

- NetCom System X-1000 transceiver test box configured with firmware version 1.17 or newer.

- PC with Fast Ether Windows (version 1.5 or newer) installed.

- Various lengths of Category 5 Unshielded Twisted-Pair (UTP) cable (1, 20, 40, 60, 80, 100, 120 and 140 meters).

- For 100BASE-FX evaluation, a fiber-optic transceiver module (HFBR-5103) and fiber-optic cable are required.

#### 2.1 Test Setup

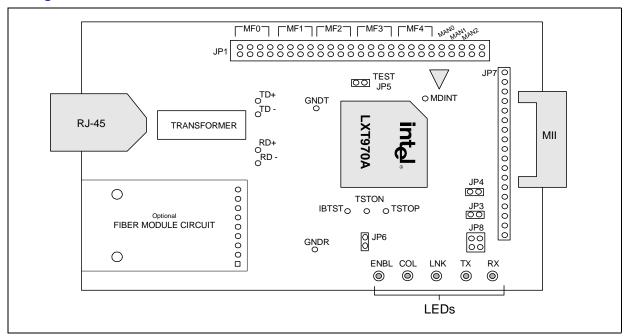

Figure 1 shows a typical test setup for the basic operation of the LXD970A. The LXD970A plugs directly into a X1000 NetCom Transceiver Test Box via a standard 40-pin MII connector that is included on the board.

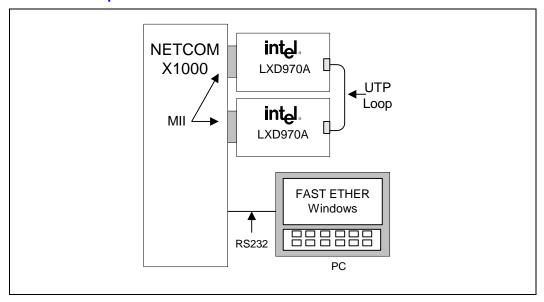

An optional test setup is shown in Figure 2 using a PC for testing additional nodes.

Note: JP3 and JP4 must be installed on the LXD970A for the Netcom System X-1000 transceiver test box to access the MII management registers inside the LXT970A.

Figure 2. Basic Test Setup

## 2.2 Loading Test File

A disk that contains the file needed for testing is included with the LXD970A demo board.

This file contains "Killer Packets" (100Tx4.s), that exhibit worst case baseline wander characteristics suitable for evaluating link performance and comparing the LXT970A to alternative products. Some devices do not adjust well over a range of cable distances. It is recommended to compare LXT970A performance to similar devices over a wide range of cable lengths.

Follow this simple procedure for loading test file into the Netcom X-1000 test box:

- · Load disk containing test pattern into computer

- Start Fast Ether Windows

- Click the "DATA PATTERN" button in the lower left of the screen

- From the Data Pattern options presented, select "CUSTOM"

- From the File menu, select "OPEN", then select the drive and directory where the test file is located. (If you are using the disk from Intel, select A:\100Tx4.s)

- When the test file is displayed on screen, select "CLOSE". This automatically downloads the test pattern to the Netcom X1000 test box

- Proceed with normal testing

Figure 3. Optional Test Setup

### 2.3 Power Supply Option

The LXD970A includes a jumper (JP8), which provides a an optional power supply source for the VCC pins; VCCA (analog supply), VCCR (receive supply), VCCT (transmit supply) and VCCD (digital supply). In the original factory configuration, this jumper is shorted by a circuit trace and all LXD970A power is supplied via the MII pin (J1). However, the circuit trace can be easily cut to provide the JP8 isolation option.

#### 2.3.1 External +5V Supply for Analog Circuitry (VCCA, VCCT and VCCR)

To provide an external +5V power supply for the LXD970A analog circuitry, proceed as follows:

- Cut the circuit trace across JP8 pins 3 and 4

- Attach an external +5V supply to JP8 pin 3

This routes the external supply to VCCA, VCCT, and VCCR (all circuits except VCCD and VCCIO). To restore to factory configuration, disconnect the external power supply and install the jumper block in JP8.

#### 2.4 Test Points

There are 9 Test Points on the LXD970A Demo Board. Table 1 describes these.

**Table 1. Test Point Descriptions**

| Label | Ref Des | Description                                                                  |

|-------|---------|------------------------------------------------------------------------------|

| TD+   | J3      | Transmit Data Output Positive - Signals transmitted from LXD970A to TP link. |

| TD-   | J4      | Transmit Data Output Negative - Signal transmitted from LXD970A to TP link.  |

| RD+   | J5      | Receive Data Input Positive - Signals received from TP network.              |

| RD-   | J6      | Receive Data Input Negative - Signals received from TP network.              |

| GNDA  | J8      | Analog Ground                                                                |

| TSTON | J9      | Test Output Negative <sup>1</sup>                                            |

| TSTOP | J10     | Test Output Positive <sup>1</sup>                                            |

| IBTST | J11     | IB Test <sup>1</sup>                                                         |

| MDINT | J12     | Management Data Interrupt <sup>2</sup> - Indicates status change.            |

<sup>1.</sup> Factory Test Only

<sup>2. 4.7</sup>k $\Omega$  pull-up to VCC needed if used

# 3.0 Jumpers

There are 7 Jumpers on the LXD970 Demo Board. Table 2 describes these jumpers and their functions.

**Table 2. Jumper Descriptions**

| Ref Des | Function                                                                                                                                                                                                            |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JP1     | <b>Hardware Control Interface:</b> Provides access to voltage sensitive manual control functions. See Tables 3, 4 and 5 for details.                                                                                |

| JP3     | <b>MDIO:</b> Connects the MDIO pin to the MII connector. With the trace cut and the jumper open, the MDIO pin can be connected to an external device.                                                               |

| JP4     | <b>MDC:</b> Connects the MDC pin to the MII connector. With the trace cut and the jumper open, the MDC pin can be connected to an external device.                                                                  |

| JP5     | <b>TEST:</b> This jumper should not be installed for normal operation. This jumper is used to put the chip into a test mode that is used to characterize the chip.                                                  |

|         | POWER DOWN: With the jumper installed the chip goes into a power down mode.                                                                                                                                         |

| JP6     | In power down mode the MII port (except MDIO and MDC), the twisted pair port and the LED pins are tristated.                                                                                                        |

| JP7     | MII: 18-pin straight header that is connected to all the MII interface signal pins. There is a ground test point next to C20 to ground probes to.                                                                   |

|         | ANALOG VCC CONNECT: Connects MII connector power to the analog portion of the chip.                                                                                                                                 |

|         | To use +5V power from MII connector:                                                                                                                                                                                |

| JP8     | No action required. The jumpers (pins 1 & 2 and 3 & 4) are shorted via a trace on the bottom of board. However, if the traces are cut, the jumpers must be installed to supply power from MII to analog VCC (VCCA). |

|         | To use alternate power supply for Analog VCC:                                                                                                                                                                       |

|         | Cut the trace on the bottom of board across pins 3 and 4 shorting JP8. With no jumpers installed, an external power can be connected. Provide an alternate power supply ( +5V) to pin 3 of JP8.                     |

# 4.0 Hardware Control Interface

#### 4.1 Multi-Function Pins

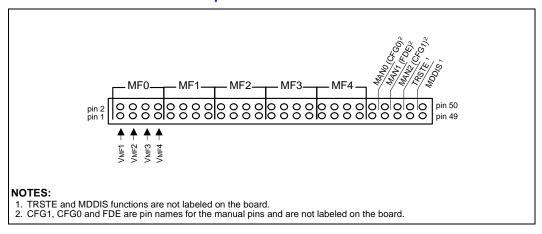

The Hardware Control Interface (JP1) provides access to the Multi-Function (MF) pins which decode 4-level supply voltages to establish two independent settings per pin. The first setting determines chip address. The second setting determines configuration of the LXD970A. The 4-level inputs referred to as VMF1, VMF2, VMF3 and VMF4 are shown in Table 3.

Table 3. MF Pins Input Voltage Levels

| Parameter             | Symbol | Min           | Max         | Units |

|-----------------------|--------|---------------|-------------|-------|

| Input Voltage Level 1 | VMF1   | Vcc - 0.5     | -           | V     |

| Input Voltage Level 2 | VMF2   | (Vcc/2) + 0.5 | Vcc - 1.2   | V     |

| Input Voltage Level 3 | VMF3   | 1.2           | Vcc/2 - 0.5 | V     |

| Input Voltage Level 4 | VMF4   | -             | 0.5         | V     |

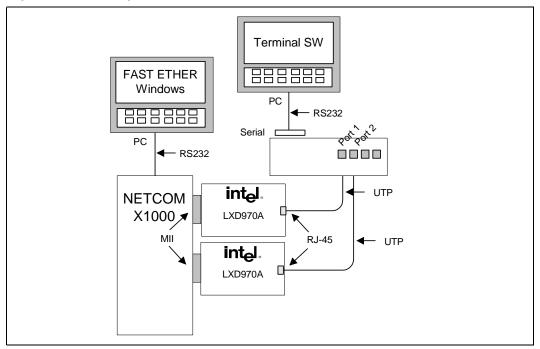

To select an Input Level place a jumper on the appropriate pins. The 4-level input pins (VMF1, VMF2, VMF3 and VMF4) are identical for each Multi-Function (MF) section. See Figure 3 for jumper placement.

Figure 4. Hardware Control Interface Jumper Placement

# 4.1.1 Function/Address Settings

The multi-function pins allow the user to enable or disable the applicable functions and determine chip address according to the input level selected. Table 4 shows the status of the function according to the (VMF) selection.

Table 4. Hardware Control Interface (JP1) Functions

|        | Address                                                                                                                                                      | Input Voltage Levels <sup>2</sup> |                           |                           |                           |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------|---------------------------|---------------------------|

| Pin    | Function                                                                                                                                                     | VMF1                              | VMF2                      | VMF3                      | VmF4                      |

|        | Address Bit 0                                                                                                                                                | 1                                 | 1                         | 0                         | 0                         |

| MF0    | Auto-Negotiation<br>Sets the initial value of bit 0.12                                                                                                       | Disabled (0.12 = 0)               | Enabled<br>(0.12 = 1)     | Enabled<br>(0.12 = 1)     | Disabled<br>(0.12 = 0)    |

|        | Address Bit 1                                                                                                                                                | 1                                 | 1                         | 0                         | 0                         |

| MF1    | Repeater / DTE Mode<br>Sets the initial value of bit 19.13                                                                                                   | DTE<br>(19.13 = 0)                | Repeater<br>(19.13 = 1)   | Repeater<br>(19.13 = 1)   | DTE<br>(19.13 = 0)        |

|        | Address Bit 2                                                                                                                                                | 1                                 | 1                         | 0                         | 0                         |

| MF2    | Nibble (4B) / Symbol (5B) Mode<br>Sets the initial value of bit 19.4                                                                                         | Nibble (4B)<br>(19.4 = 0)         | Symbol (5B)<br>(19.4 = 1) | Symbol (5B)<br>(19.4 = 1) | Nibble (4B)<br>(19.4 = 0) |

|        | Address Bit 3                                                                                                                                                | 1                                 | 1                         | 0                         | 0                         |

| MF3    | Scrambler Operation Sets the initial value of bit 19.3                                                                                                       | Enabled (19.3 = 0)                | Bypassed<br>(19.3 = 1)    | Bypassed<br>(19.3 = 1)    | Enabled (19.3 = 0)        |

|        | Address Bit 4                                                                                                                                                | 1                                 | 1                         | 0                         | 0                         |

| MF4    | If Auto-Negotiate Enabled via MF0, MF4 works in combination with MAN2 (CFG1) to control operating speed advertisement capabilities. See Table 5 for details. |                                   |                           |                           |                           |

| 1011 4 | If Auto-Negotiate Disabled<br>Then TX/F Mode<br>Sets the initial value of bit 19.2                                                                           | 100TX<br>(19.2 = 0)               | 100FX<br>(19.2 = 1)       | 100FX<br>(19.2 = 1)       | 100TX<br>(19.2 = 0)       |

**Table 5. Operating Speed Advertisement Settings**

| MF4 Input<br>Voltage Levels <sup>1</sup>                      | MAN2<br>(CFG1)       | Function                                      |  |  |

|---------------------------------------------------------------|----------------------|-----------------------------------------------|--|--|

| If Auto-Negotiate Enabled via MF0                             |                      |                                               |  |  |

| VMF1, VMF4                                                    | Jumper Not Installed | Advertise all capabilities, Ignore MAN1 (FDE) |  |  |

| VMF1, VMF4                                                    | Jumper Installed     | Advertise 10 Mbps only, Follow MAN1 (FDE)     |  |  |

| VMF2, VMF3                                                    | Jumper Not Installed | Advertise 100 Mbps only, Follow MAN1 (FDE)    |  |  |

| VMF2, VMF3                                                    | Jumper Installed     | Advertise 10/100 Mbps, Follow MAN1 (FDE)      |  |  |

| 1. Input Voltage Levels (VMF1, VMF2, VMF3, VMF4) for MF pins. |                      |                                               |  |  |

#### 4.1.2 Additional Jumper Functions

In addition to the MF pins, the Hardware Control Interface (JP1) contains 10 pins, (#41 - #50) that are labeled as MAN0, MAN1, MAN2, TRSTE and MDDIS, (Note: TRSTE and MDDIS are not labeled on the demo board). MAN0 = CFG0, MAN1 = FDE and MAN2 = CFG1. The Manual pins control the status of the applicable function by installing or removing a jumper. See Table 6 for function status.

Table 6. Additional JP1 Jumper Functions

| Jumper Label        | Function                                                              | Status                                                                                                                                        | Jumper<br>Installed | Jumper Not<br>Installed |

|---------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------|

|                     | Restart Negotiation                                                   | Enable                                                                                                                                        |                     | Х                       |

| MAN0                | (when Auto-Neg enabled) <sup>1</sup>                                  | Disable                                                                                                                                       | Χ                   |                         |

| (CFG0)              | Speed Select                                                          | 10Mbps                                                                                                                                        |                     | Х                       |

|                     | (when Auto-Neg disabled) <sup>1</sup>                                 | 100Mbps                                                                                                                                       | Х                   |                         |

| MAN1                | Full Dumley                                                           | Enable                                                                                                                                        | Χ                   |                         |

| (FDE)               | Full Duplex                                                           | Disable                                                                                                                                       |                     | Х                       |

| MAN2                | Speed Advertisement Capabilities (when Auto-Neg enabled) <sup>1</sup> | When Auto-Neg enabled, MAN2 (CFG1) works in combination with MF4 to control operating speed advertising capabilities. See Table 5 for details |                     |                         |

| (0=0.1)             | Link Test                                                             |                                                                                                                                               |                     |                         |

| (CFG1)              | Link Test                                                             | Enable                                                                                                                                        |                     | Х                       |

| (CFG1)              | <b>Link Test</b><br>(when Auto-Neg disabled) <sup>1</sup>             | Enable<br>Disable                                                                                                                             | Х                   |                         |

| (CFG1)              |                                                                       |                                                                                                                                               |                     |                         |

| (CFG1)  Not Labeled |                                                                       | Disable                                                                                                                                       | X<br>X              |                         |

| ,                   | (when Auto-Neg disabled) <sup>1</sup>                                 | Disable<br>Tristates                                                                                                                          |                     | X                       |

| Not Labeled         | (when Auto-Neg disabled) <sup>1</sup> Tristate                        | Disable Tristates MII Data Interface                                                                                                          |                     |                         |

| Not Labeled         | (when Auto-Neg disabled) <sup>1</sup> Tristate                        | Disable Tristates MII Data Interface Normal                                                                                                   |                     | X                       |

#### 4.2 **LED Indicators**

There are 5 status LEDs on the Demo Board. Refer to Table 7 for LED descriptions.

**Table 7. LED Descriptions**

| Label | Ref Des | Description                                     |

|-------|---------|-------------------------------------------------|

| ENBL  | D1      | Line Speed. Indicates 100Mbps operation         |

| COL   | D2      | Collision. Indicates collision                  |

| LNK   | D3      | Link. Indicates connection                      |

| TX    | D4      | Transmit Data. Indicates data being transmitted |

| RX    | D5      | Receive Data. Indicates data being received     |

Figure 5. LXD970A Schematic